Difference between revisions of "Computer Architecture"

Joel-chung (talk | contribs) |

|||

| (21 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

== Curriculum == | == Curriculum == | ||

{{MerlinCurriculumData|{{ROOTPAGENAME}}}} | {{MerlinCurriculumData|{{ROOTPAGENAME}}}} | ||

== Introduction == | == Introduction == | ||

Computers are amazing devices and play a significant role in nearly everything that we do. While seemingly complex, the basic architecture of a computer is | Computers are amazing devices and play a significant role in nearly everything that we do. While seemingly complex, the basic architecture of a computer is straightforward. In this experience, we'll take a look at memory, the central processing unit, the arithmetic logic unit, data and address buses, and examine how a computer processes instructions. | ||

== Memory == | == Memory == | ||

[[File:DDR RAM-2.jpg|thumb|left|link=|DDR RAM-2]] | [[File:DDR RAM-2.jpg|thumb|left|link=|DDR RAM-2]] | ||

[[file:Memory Word.png|thumb|right|link=|Memory | [[file:Memory Word.png|thumb|right|link=|Memory word]] | ||

=== Bit Width === | === Bit Width === | ||

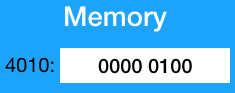

Computer memory, sometimes referred to as '''primary storage''', is divided into units called '''word'''s. Each word consists of multiple '''bit'''s (binary digits). Each bit is preserved through the use of a Flip Flop, such as the '''D-type Flip Flop''' described in [[W1018 | Computer memory, sometimes referred to as '''primary storage''', is divided into units called '''word'''s. Each word consists of multiple '''bit'''s (binary digits). Each bit is preserved through the use of a Flip Flop, such as the '''D-type Flip Flop''' described in [[W1018]]. The bits are ordered into a fixed-size piece of data (a '''word''') and accessed as a single unit. In the image each word consists of 8 bits, and we refer to this as the '''bit-width''' of the machine. (For example, many of you may have "64-bit machines." The 64 bits refer to the bit-width of the words in memory and the ability of the processor to handle each word as a single unit.) '''yip yap pip pap''' | ||

<br clear='all' /> | <br clear='all' /> | ||

=== Addressable Memory === | === Addressable Memory === | ||

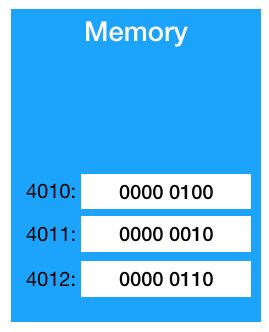

Accessing memory requires that | Accessing memory requires that every word has a unique address, which we call the '''memory address'''. Addresses are generally linear, beginning at zero, and increase for each available word in memory. In the image, the address is shown on the left-hand side as 4010. | ||

[[file:Memory Words.png|thumb|left|link=|Memory | [[file:Memory Words.png|thumb|left|link=|Memory addresses]] | ||

The image on the left shows how addresses increase sequentially. | The image on the left shows how addresses increase sequentially. Three words are shown, with addresses (in hexadecimal) of 4010, 4011, and 4012. | ||

<br clear='all' /> | <br clear='all' /> | ||

=== The Address Bus === | === The Address Bus === | ||

[[file:Memory Address Bus.png|thumb|right|link=|Memory | [[file:Memory Address Bus.png|thumb|right|link=|Memory address bus]] | ||

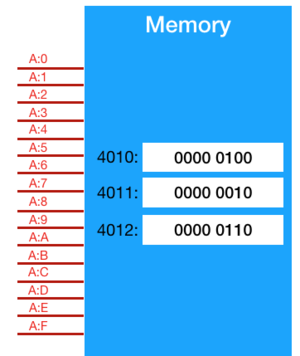

The CPU accesses one word of memory at any | The CPU accesses one word of memory at any time. To specify ''which'' of the many words should be accessed, the address is specified on the '''address bus'''. The bus specifies, in binary, the address in which we are interested. Each "wire" is either high or low. In combination, the high/low values on the bus indicate the address. As usual, the least significant bit is labeled as 0 (A:0). | ||

<br clear='all' /> | <br clear='all' /> | ||

=== The Data Bus === | === The Data Bus === | ||

[[file:Memory Data Bus.png|thumb|left|link=|Memory | [[file:Memory Data Bus.png|thumb|left|link=|Memory data bus]] | ||

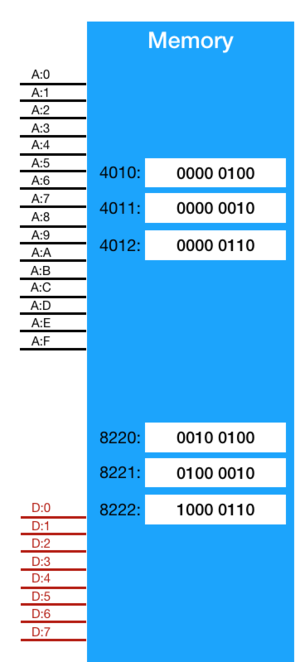

Although the ''address bus'' specifies the address in which we are interested, it is the '''data bus''' that actually moves the data from/to primary storage. Note that in the case of our example, 16 bits are required on the ''address bus'' to specify the word in which we are interested, because this computer can access <math>2^{16}</math> words. The data bus, however, is only 8 bits wide, because each word contains exactly 8 bits. | |||

<br clear='all' /> | <br clear='all' /> | ||

=== The Read/Write Flag === | === The Read/Write Flag === | ||

The data bus can either transfer data '''to''' main memory ''or'' '''from''' main memory, but not both at the same time. | The data bus can either transfer data '''to''' main memory ''or'' '''from''' main memory, but not both at the same time. To specify the direction, we use a '''read/write flag'''. (A ''flag'' is a term that generally represents exactly one of two possible states.) | ||

[[file:Memory ReadWrite Flag.png|thumb|right|link=|Memory | [[file:Memory ReadWrite Flag.png|thumb|right|link=|Memory read/write flag]] | ||

<br clear='all' /> | <br clear='all' /> | ||

== The Arithmetic Logic Unit == | == The Arithmetic Logic Unit == | ||

The '''Arithmetic Logic Unit''', often abbreviated as '''ALU''', is responsible for accepting one or two operands, performing either an arithmetic or logical operation, and then providing the result. | The '''Arithmetic Logic Unit''', often abbreviated as '''ALU''', is responsible for accepting one or two operands, performing either an arithmetic or logical operation, and then providing the result. These calculations are performed using the logic gates that we've previously studied, such as AND, OR, NOT, XOR, and binary addition. | ||

{{ResponsiveImage|[[file:Arithmetic Logic Unit.png|link=|Arithmetic | {{MerlinNoteFromEditor|Should the NOT be NOR instead just above in that last sentence?}} | ||

A '''register''' is a quickly accessible location | |||

{{ResponsiveImage|[[file:Arithmetic Logic Unit.png|link=|Arithmetic logic unit]]}} | |||

A '''register''' is a quickly accessible location that can be directly accessed in a process that is ''much faster'' than accessing main memory. In the case of the ALU, it has two input registers and one output register. To perform an operation, the input operands are sent to the input registers (Register A and Register B), and, after a brief '''propagation delay''', the output is made available in the output register. | |||

== The Central Processing Unit == | == The Central Processing Unit == | ||

[[file:Sun_UltraSPARCII.jpg|right|thumb|link=|Central Processing Unit]] | [[file:Sun_UltraSPARCII.jpg|right|thumb|link=|Central Processing Unit]] | ||

The '''Central Processing Unit''', often abbreviated as '''CPU''', is responsible for executing the instructions of a program, including those of the operating system. | The '''Central Processing Unit''', often abbreviated as '''CPU''', is responsible for executing the instructions of a program, including those of the operating system. | ||

The CPU contains several internal registers. Some of these registers are ''general purpose'' and | The CPU contains several internal registers. Some of these registers are ''general purpose'' and can be used for temporarily holding operands. In our example CPU, the general purpose registers are labeled as AX, BX, and CX. Other registers have a special, dedicated purpose. In our example CPU, these are: | ||

* The '''instruction register''': It is responsible for processing an instruction from memory by understanding what steps are required to realize the specified operation. | * The '''instruction register''': It is responsible for processing an instruction from memory by understanding what steps are required to realize the specified operation. | ||

* The '''program counter''' or '''PC''': It is responsible for pointing to the next instruction to be fetched from main memory. | * The '''program counter''' or '''PC''': It is responsible for pointing to the next instruction to be fetched from main memory. As such, the width of this register will be the same as the width of the address bus. | ||

* The '''stack pointer''': It is responsible for pointing to the next free position on the stack (a data structure that we'll cover in a later experience). | * The '''stack pointer''': It is responsible for pointing to the next free position on the stack (a data structure that we'll cover in a later experience). | ||

* The '''status register''': It contains the status of a recent operation, such as | * The '''status register''': It contains the status of a recent operation, such as if the result is zero, negative, or if there was an overflow condition. | ||

{{GoingDeeper| | {{GoingDeeper| | ||

For | For more information regarding the ''status register'', see [[W1151_Conditional_and_Flow_Chart#Jump_Instructions|{{Cyan|Jump Instructions}}]]. | ||

}} | }} | ||

<br clear='all'/> | <br clear='all'/> | ||

| Line 50: | Line 54: | ||

== The Instruction Cycle == | == The Instruction Cycle == | ||

Digital computers generally follow a standard cycle, called the '''Fetch-Decode-Execute''' cycle. It is the basic operational process of a computer. From boot-up until shut down, the CPU | Digital computers generally follow a standard cycle, called the '''Fetch-Decode-Execute''' cycle. It is the basic operational process of a computer. From boot-up until shut down, the CPU retrieves a program instruction from memory, determines what the instruction means and how to fulfill that instruction, and then executes the necessary steps before repeating the cycle. | ||

=== Fetch === | === Fetch === | ||

The next instruction is fetched from the memory address that is | The next instruction is fetched from the memory address that is stored in the program counter (PC). The instruction is stored in the instruction register (IR). The PC is then incremented. | ||

program counter (PC). The instruction is stored in the instruction register (IR). The PC is | |||

then incremented. | |||

=== Decode === | === Decode === | ||

The instruction is decoded by the instruction decoder. | The instruction is decoded by the instruction decoder. If additional memory accesses are required to read operands, it happens here. | ||

=== Execute === | === Execute === | ||

The instruction is executed by the control unit | The instruction is executed by the control unit that sends a sequence of signals to the relevant function units of the CPU such as reading values from registers, passing them to the ALU to perform mathematical or logical functions, and writing the results back to a register. The control unit can accept input from the ALU and update the program counter to a different address if so indicated before continuing to the next cycle.

| ||

the relevant function units of the CPU such as reading values from registers, passing them to the ALU to perform mathematical or logical functions, and writing the results back to a register. The control unit | |||

== An Example == | == An Example == | ||

Let's consider an example of what occurs inside the computer when we execute the following:<br/> | Let's consider an example of what occurs inside the computer when we execute the following:<br/> | ||

<math>x = a + b</math><br/> | <math>x = a + b</math><br/> | ||

Let's assume that the variable <math>a</math> is stored in location 0x4010, <math>b</math> is stored in location 0x4011, and <math>c</math> is stored in location 0x4012. | Let's assume that the variable <math>a</math> is stored in location 0x4010, <math>b</math> is stored in location 0x4011, and <math>c</math> is stored in location 0x4012. This single statement is essentially instructing the computer to: | ||

# Access the variable <math>a</math> | # Access the variable <math>a</math> | ||

# Access the variable <math>b</math> | # Access the variable <math>b</math> | ||

# Add the values of <math>a</math> and <math>b</math> | # Add the values of <math>a</math> and <math>b</math> | ||

# Store the sum in the variable <math>x</math> | # Store the sum in the variable <math>x</math> | ||

In the computer, this might appear as:<br/> | |||

<pre> | <pre> | ||

LDAX [4010] | LDAX [4010] | ||

| Line 77: | Line 77: | ||

STAX [4012] | STAX [4012] | ||

</pre> | </pre> | ||

The actions | The actions the CPU carries out will be as follows: | ||

# Load the AX register with the value stored in main memory at address 0x4010 | # Load the AX register with the value stored in main memory at address 0x4010 | ||

## Fetch | ## Fetch | ||

### The address in the | ### The address in the PC is placed on the memory address bus | ||

### The address is carried across the address bus to main memory | ### The address is carried across the address bus to main memory | ||

### Set the memory read/write flag to read | ### Set the memory read/write flag to read | ||

### The instruction | ### The instruction at the specified address is placed on the memory data bus | ||

### The instruction is carried across the data bus to the memory data register | ### The instruction is carried across the data bus to the memory data register | ||

### The CPU transfers the instruction from the memory data register to the | ### The CPU transfers the instruction from the memory data register to the IR | ||

### The address in the PC is incremented | ### The address in the PC is incremented | ||

## Decode | ## Decode | ||

| Line 94: | Line 94: | ||

### The address is carried across the address bus to main memory | ### The address is carried across the address bus to main memory | ||

### Set the memory read/write flag to read | ### Set the memory read/write flag to read | ||

### The data | ### The data at the address 0x4010 are placed on the memory data bus | ||

### The data are carried across the data bus to the memory data register | ### The data are carried across the data bus to the memory data register | ||

### The CPU transfers the data from the memory data register to the AX register | ### The CPU transfers the data from the memory data register to the AX register | ||

# Load the BX register with the value stored in main memory at address 0x4011 | # Load the BX register with the value stored in main memory at address 0x4011 | ||

## Fetch | ## Fetch | ||

### The address in the | ### The address in the PC is placed on the memory address bus | ||

### The address is carried across the address bus to main memory | ### The address is carried across the address bus to main memory | ||

### Set the memory read/write flag to read | ### Set the memory read/write flag to read | ||

### The instruction | ### The instruction at the specified address is placed on the memory data bus | ||

### The instruction is carried across the data bus to the memory data register | ### The instruction is carried across the data bus to the memory data register | ||

### The CPU transfers the instruction from the memory data register to the | ### The CPU transfers the instruction from the memory data register to the IR | ||

### The address in the PC is incremented | ### The address in the PC is incremented | ||

## Decode | ## Decode | ||

| Line 113: | Line 113: | ||

### The address is carried across the address bus to main memory | ### The address is carried across the address bus to main memory | ||

### Set the memory read/write flag to read | ### Set the memory read/write flag to read | ||

### The data | ### The data at the address 0x4011 are placed on the memory data bus | ||

### The data are carried across the data bus to the memory data register | ### The data are carried across the data bus to the memory data register | ||

### The CPU transfers the data from the memory data register to the BX register | ### The CPU transfers the data from the memory data register to the BX register | ||

# Add the current contents of AX to BX, and place the sum in AX | # Add the current contents of AX to BX, and place the sum in AX | ||

## Fetch | ## Fetch | ||

### The address in the | ### The address in the PC is placed on the memory address bus | ||

### The address is carried across the address bus to main memory | ### The address is carried across the address bus to main memory | ||

### Set the memory read/write flag to read | ### Set the memory read/write flag to read | ||

### The instruction | ### The instruction at the specified address is placed on the memory data bus | ||

### The instruction is carried across the data bus to the memory data register | ### The instruction is carried across the data bus to the memory data register | ||

### The CPU transfers the instruction from the memory data register to the | ### The CPU transfers the instruction from the memory data register to the IR | ||

### The address in the PC is incremented | ### The address in the PC is incremented | ||

## Decode | ## Decode | ||

### The CPU decodes the instruction in the | ### The CPU decodes the instruction in the IR | ||

### The CPU executes a plan to fulfill the instruction | ### The CPU executes a plan to fulfill the instruction | ||

## Execute | ## Execute | ||

| Line 132: | Line 132: | ||

### The CPU transfers the data from the BX register to the ALU's Register B | ### The CPU transfers the data from the BX register to the ALU's Register B | ||

### The CPU uses a combination of control signals to specify that it's interested in the ''add'' function | ### The CPU uses a combination of control signals to specify that it's interested in the ''add'' function | ||

### The ALU places the sum of Register A and Register B into its | ### The ALU places the sum of Register A and Register B into its output register | ||

### The CPU transfers the contents of the ALU's | ### The CPU transfers the contents of the ALU's output register to the AX register | ||

# Store the contents of register AX into main memory at address 0x4012 | # Store the contents of register AX into main memory at address 0x4012 | ||

## Fetch | ## Fetch | ||

### The address in the | ### The address in the PC is placed on the memory address bus | ||

### The address is carried across the address bus to main memory | ### The address is carried across the address bus to main memory | ||

### Set the memory read/write flag to read | ### Set the memory read/write flag to read | ||

### The instruction | ### The instruction at the specified address is placed on the memory data bus | ||

### The instruction is carried across the data bus to the memory data register | ### The instruction is carried across the data bus to the memory data register | ||

### The CPU transfers the instruction from the memory data register to the | ### The CPU transfers the instruction from the memory data register to the IR | ||

### The address in the PC is incremented | ### The address in the PC is incremented | ||

## Decode | ## Decode | ||

### The CPU decodes the instruction in the | ### The CPU decodes the instruction in the IR | ||

### The CPU executes a plan to fulfill the instruction | ### The CPU executes a plan to fulfill the instruction | ||

## Execute | ## Execute | ||

| Line 157: | Line 157: | ||

{{KeyConcepts| | {{KeyConcepts| | ||

* Main memory in a computer is sometimes referred to as '''primary storage''' | * Main memory in a computer is sometimes referred to as '''primary storage''' | ||

* On September 26th and 27th, 2023, the quiz will be '''open note''' | |||

* Main memory is divided into fixed-size pieces of data called '''words''' | * Main memory is divided into fixed-size pieces of data called '''words''' | ||

* Each word consists of multiple '''bits''' (binary digits) | * Each word consists of multiple '''bits''' (binary digits) | ||

* The number of bits in a word is referred to as '''bit-width''' | * The number of bits in a word is referred to as '''bit-width''' | ||

* Each bit | * Each bit can be represented by a single '''D-type Flip Flop''' | ||

* Accessing memory requires that every word has a unique address; we call this the '''memory address''' | * Accessing memory requires that every word has a unique address; we call this the '''memory address''' | ||

* The '''address bus''' transfers the requested address from the CPU to main memory | * The '''address bus''' transfers the requested address from the CPU to main memory | ||

| Line 166: | Line 167: | ||

* The '''read/write flag''' specifies whether we want to ''read from'' memory or ''write to'' memory | * The '''read/write flag''' specifies whether we want to ''read from'' memory or ''write to'' memory | ||

* The '''Arithmetic Logic Unit''' (often abbreviated '''ALU''') performs a calculation on one or two operands | * The '''Arithmetic Logic Unit''' (often abbreviated '''ALU''') performs a calculation on one or two operands | ||

** The calculations are performed using logic gates such as AND, OR, NOT, XOR, and binary addition | ** The calculations are performed using logic gates such as AND, OR, NOT, XOR, and binary addition {{MerlinNoteFromEditor|Should that NOT be NOR instead, just above here?}} | ||

* A '''register''' is a quickly accessible location | * A '''register''' is a quickly accessible location that can be directly accessed in a process that is ''much faster'' than accessing main memory | ||

* The ALU receives input from a local ''Register A'' and ''Register B''. | * The ALU receives input from a local ''Register A'' and ''Register B''. When the ALU completes its calculation, it places the result in its ''Output Register''. | ||

* The '''Central Processing Unit''', often abbreviated as '''CPU''', is responsible for executing the instructions of a program | * The '''Central Processing Unit''', often abbreviated as '''CPU''', is responsible for executing the instructions of a program | ||

* The ''CPU'' contains several internal registers: | * The ''CPU'' contains several internal registers: | ||

** The '''Instruction Register''', often | ** The '''Instruction Register''', often abbreviated as '''IR''', is responsible for processing an instruction from memory and helps decode the instruction | ||

** The '''Program Counter''', often abbreviated as '''PC''', is responsible for pointing to the next instruction to be fetched from memory | ** The '''Program Counter''', often abbreviated as '''PC''', is responsible for pointing to the next instruction to be fetched from memory | ||

** The '''Stack Pointer''' points to the next free position on the stack | ** The '''Stack Pointer''' points to the next free position on the stack | ||

** The '''Status Register''' contains the status of a recent operation, such as whether | ** The '''Status Register''' contains the status of a recent operation, such as whether the result is zero, negative, or if there was an overflow condition | ||

* The '''instruction cycle''' consists of three steps: | * The '''instruction cycle''' consists of three steps: | ||

** '''Fetch''': The next instruction is fetched from the memory address | ** '''Fetch''': The next instruction is fetched from the memory address stored in the ''PC'' and placed in the '''IR'''. The ''PC'' is then incremented. | ||

** '''Decode''': The instruction is decoded. | ** '''Decode''': The instruction is decoded. If additional memory accesses are required to read operands, it happens here. | ||

** '''Execute''': The instruction is executed by the control unit making use of the ALU as required. | ** '''Execute''': The instruction is executed by the control unit making use of the ALU as required. The PC can also be updated if so indicated. | ||

}} | }} | ||

| Line 190: | Line 191: | ||

* [http://www.baltissen.org/newhtm/ttl6502.htm TTL 6502] | * [http://www.baltissen.org/newhtm/ttl6502.htm TTL 6502] | ||

* [https://en.wikipedia.org/wiki/Computer_memory Computer Memory] | * [https://en.wikipedia.org/wiki/Computer_memory Computer Memory] | ||

* [https://en.wikipedia.org/wiki/Arithmetic_logic_unit | * [https://en.wikipedia.org/wiki/Arithmetic_logic_unit Arithmetic Logic Unit] | ||

Latest revision as of 10:53, 11 December 2023

Curriculum[edit]

| Coder Merlin™ Computer Science Curriculum Data | |

|

Unit: Experience Name: Computer Architecture () Next Experience: () Knowledge and skills: noneSome use of "" in your query was not closed by a matching "". Topic areas: none Classroom time (average): Study time (average): Successful completion requires knowledge: none Successful completion requires skills: none |

Introduction[edit]

Computers are amazing devices and play a significant role in nearly everything that we do. While seemingly complex, the basic architecture of a computer is straightforward. In this experience, we'll take a look at memory, the central processing unit, the arithmetic logic unit, data and address buses, and examine how a computer processes instructions.

Memory[edit]

Bit Width[edit]

Computer memory, sometimes referred to as primary storage, is divided into units called words. Each word consists of multiple bits (binary digits). Each bit is preserved through the use of a Flip Flop, such as the D-type Flip Flop described in W1018. The bits are ordered into a fixed-size piece of data (a word) and accessed as a single unit. In the image each word consists of 8 bits, and we refer to this as the bit-width of the machine. (For example, many of you may have "64-bit machines." The 64 bits refer to the bit-width of the words in memory and the ability of the processor to handle each word as a single unit.) yip yap pip pap

Addressable Memory[edit]

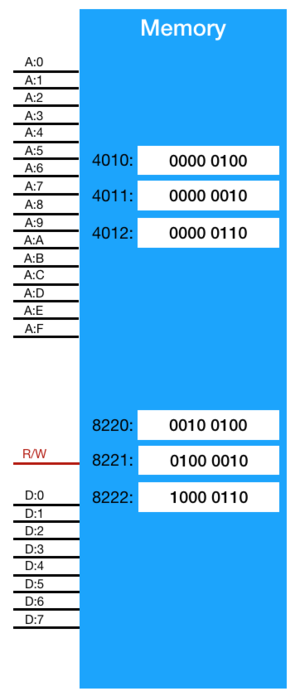

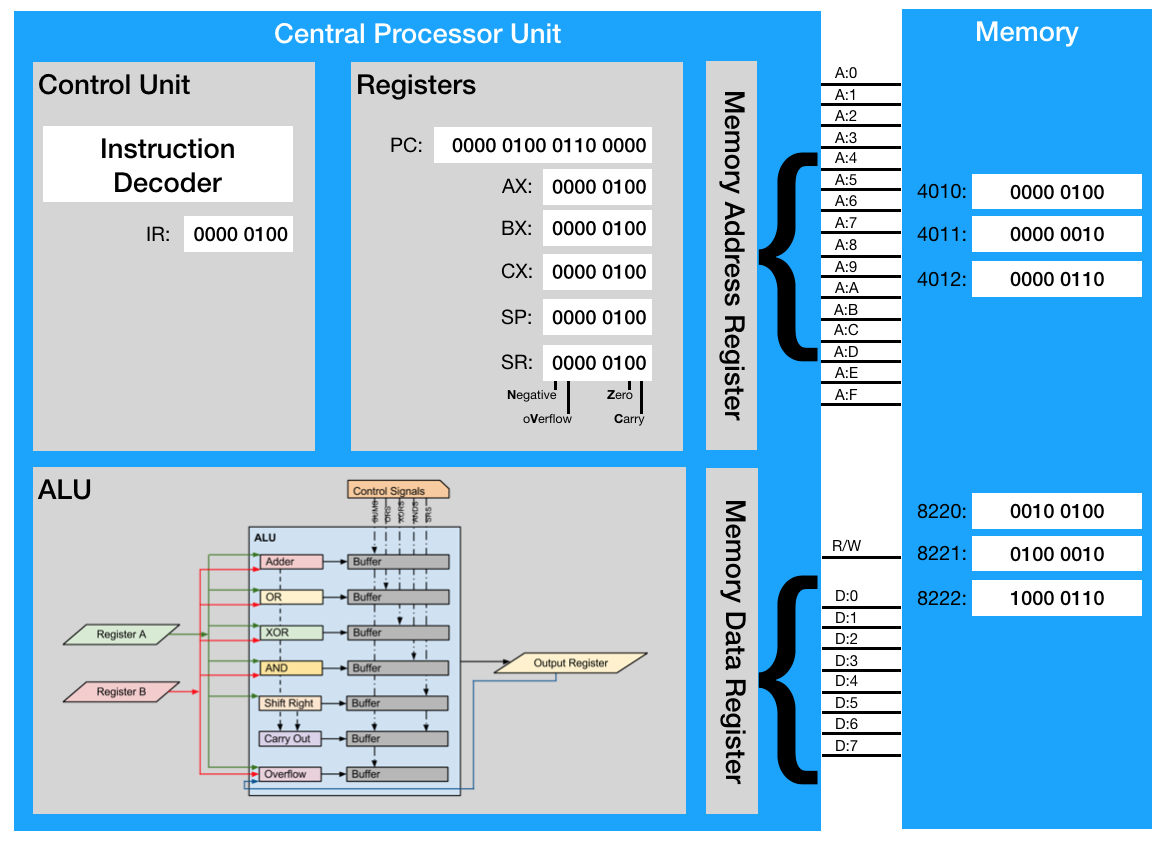

Accessing memory requires that every word has a unique address, which we call the memory address. Addresses are generally linear, beginning at zero, and increase for each available word in memory. In the image, the address is shown on the left-hand side as 4010.

The image on the left shows how addresses increase sequentially. Three words are shown, with addresses (in hexadecimal) of 4010, 4011, and 4012.

The Address Bus[edit]

The CPU accesses one word of memory at any time. To specify which of the many words should be accessed, the address is specified on the address bus. The bus specifies, in binary, the address in which we are interested. Each "wire" is either high or low. In combination, the high/low values on the bus indicate the address. As usual, the least significant bit is labeled as 0 (A:0).

The Data Bus[edit]

Although the address bus specifies the address in which we are interested, it is the data bus that actually moves the data from/to primary storage. Note that in the case of our example, 16 bits are required on the address bus to specify the word in which we are interested, because this computer can access words. The data bus, however, is only 8 bits wide, because each word contains exactly 8 bits.

The Read/Write Flag[edit]

The data bus can either transfer data to main memory or from main memory, but not both at the same time. To specify the direction, we use a read/write flag. (A flag is a term that generally represents exactly one of two possible states.)

The Arithmetic Logic Unit[edit]

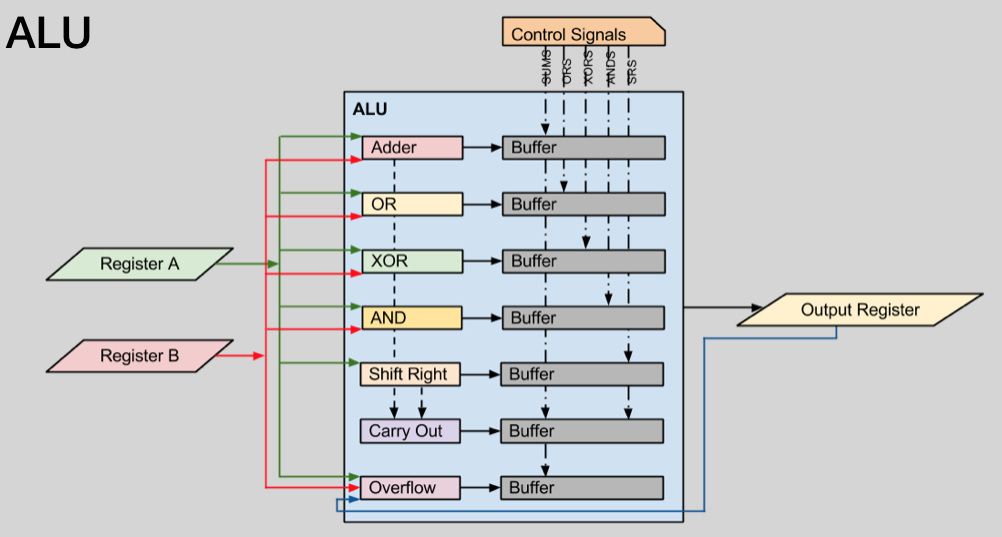

The Arithmetic Logic Unit, often abbreviated as ALU, is responsible for accepting one or two operands, performing either an arithmetic or logical operation, and then providing the result. These calculations are performed using the logic gates that we've previously studied, such as AND, OR, NOT, XOR, and binary addition.

This article can be improved by: Should the NOT be NOR instead just above in that last sentence?

A register is a quickly accessible location that can be directly accessed in a process that is much faster than accessing main memory. In the case of the ALU, it has two input registers and one output register. To perform an operation, the input operands are sent to the input registers (Register A and Register B), and, after a brief propagation delay, the output is made available in the output register.

The Central Processing Unit[edit]

The Central Processing Unit, often abbreviated as CPU, is responsible for executing the instructions of a program, including those of the operating system. The CPU contains several internal registers. Some of these registers are general purpose and can be used for temporarily holding operands. In our example CPU, the general purpose registers are labeled as AX, BX, and CX. Other registers have a special, dedicated purpose. In our example CPU, these are:

- The instruction register: It is responsible for processing an instruction from memory by understanding what steps are required to realize the specified operation.

- The program counter or PC: It is responsible for pointing to the next instruction to be fetched from main memory. As such, the width of this register will be the same as the width of the address bus.

- The stack pointer: It is responsible for pointing to the next free position on the stack (a data structure that we'll cover in a later experience).

- The status register: It contains the status of a recent operation, such as if the result is zero, negative, or if there was an overflow condition.

For more information regarding the status register, see Jump Instructions.

The Instruction Cycle[edit]

Digital computers generally follow a standard cycle, called the Fetch-Decode-Execute cycle. It is the basic operational process of a computer. From boot-up until shut down, the CPU retrieves a program instruction from memory, determines what the instruction means and how to fulfill that instruction, and then executes the necessary steps before repeating the cycle.

Fetch[edit]

The next instruction is fetched from the memory address that is stored in the program counter (PC). The instruction is stored in the instruction register (IR). The PC is then incremented.

Decode[edit]

The instruction is decoded by the instruction decoder. If additional memory accesses are required to read operands, it happens here.

Execute[edit]

The instruction is executed by the control unit that sends a sequence of signals to the relevant function units of the CPU such as reading values from registers, passing them to the ALU to perform mathematical or logical functions, and writing the results back to a register. The control unit can accept input from the ALU and update the program counter to a different address if so indicated before continuing to the next cycle.

An Example[edit]

Let's consider an example of what occurs inside the computer when we execute the following:

Let's assume that the variable is stored in location 0x4010, is stored in location 0x4011, and is stored in location 0x4012. This single statement is essentially instructing the computer to:

- Access the variable

- Access the variable

- Add the values of and

- Store the sum in the variable

In the computer, this might appear as:

LDAX [4010] LDBX [4011] ADDBX STAX [4012]

The actions the CPU carries out will be as follows:

- Load the AX register with the value stored in main memory at address 0x4010

- Fetch

- The address in the PC is placed on the memory address bus

- The address is carried across the address bus to main memory

- Set the memory read/write flag to read

- The instruction at the specified address is placed on the memory data bus

- The instruction is carried across the data bus to the memory data register

- The CPU transfers the instruction from the memory data register to the IR

- The address in the PC is incremented

- Decode

- The CPU decodes the instruction in the instruction register

- The CPU executes a plan to fulfill the instruction

- Execute

- Place the address 0x4010 in the memory address register

- The address is carried across the address bus to main memory

- Set the memory read/write flag to read

- The data at the address 0x4010 are placed on the memory data bus

- The data are carried across the data bus to the memory data register

- The CPU transfers the data from the memory data register to the AX register

- Fetch

- Load the BX register with the value stored in main memory at address 0x4011

- Fetch

- The address in the PC is placed on the memory address bus

- The address is carried across the address bus to main memory

- Set the memory read/write flag to read

- The instruction at the specified address is placed on the memory data bus

- The instruction is carried across the data bus to the memory data register

- The CPU transfers the instruction from the memory data register to the IR

- The address in the PC is incremented

- Decode

- The CPU decodes the instruction in the instruction register

- The CPU executes a plan to fulfill the instruction

- Execute

- Place the address 0x4011 in the memory address register

- The address is carried across the address bus to main memory

- Set the memory read/write flag to read

- The data at the address 0x4011 are placed on the memory data bus

- The data are carried across the data bus to the memory data register

- The CPU transfers the data from the memory data register to the BX register

- Fetch

- Add the current contents of AX to BX, and place the sum in AX

- Fetch

- The address in the PC is placed on the memory address bus

- The address is carried across the address bus to main memory

- Set the memory read/write flag to read

- The instruction at the specified address is placed on the memory data bus

- The instruction is carried across the data bus to the memory data register

- The CPU transfers the instruction from the memory data register to the IR

- The address in the PC is incremented

- Decode

- The CPU decodes the instruction in the IR

- The CPU executes a plan to fulfill the instruction

- Execute

- The CPU transfers the data from the AX register to the ALU's Register A

- The CPU transfers the data from the BX register to the ALU's Register B

- The CPU uses a combination of control signals to specify that it's interested in the add function

- The ALU places the sum of Register A and Register B into its output register

- The CPU transfers the contents of the ALU's output register to the AX register

- Fetch

- Store the contents of register AX into main memory at address 0x4012

- Fetch

- The address in the PC is placed on the memory address bus

- The address is carried across the address bus to main memory

- Set the memory read/write flag to read

- The instruction at the specified address is placed on the memory data bus

- The instruction is carried across the data bus to the memory data register

- The CPU transfers the instruction from the memory data register to the IR

- The address in the PC is incremented

- Decode

- The CPU decodes the instruction in the IR

- The CPU executes a plan to fulfill the instruction

- Execute

- Place the address 0x4012 in the memory address register

- The address is carried across the address bus to main memory

- Place the contents of the AX register into the memory data register

- The data are carries across the data bus to main memory

- Set the memory read/write flag to write

- The contents of memory data register are written (stored) in main memory at address 0x4012

- Fetch

Key Concepts[edit]

- Main memory in a computer is sometimes referred to as primary storage

- On September 26th and 27th, 2023, the quiz will be open note

- Main memory is divided into fixed-size pieces of data called words

- Each word consists of multiple bits (binary digits)

- The number of bits in a word is referred to as bit-width

- Each bit can be represented by a single D-type Flip Flop

- Accessing memory requires that every word has a unique address; we call this the memory address

- The address bus transfers the requested address from the CPU to main memory

- The data bus transfers data to/from main memory

- The read/write flag specifies whether we want to read from memory or write to memory

- The Arithmetic Logic Unit (often abbreviated ALU) performs a calculation on one or two operands

- The calculations are performed using logic gates such as AND, OR, NOT, XOR, and binary addition

This article can be improved by: Should that NOT be NOR instead, just above here?

- A register is a quickly accessible location that can be directly accessed in a process that is much faster than accessing main memory

- The ALU receives input from a local Register A and Register B. When the ALU completes its calculation, it places the result in its Output Register.

- The Central Processing Unit, often abbreviated as CPU, is responsible for executing the instructions of a program

- The CPU contains several internal registers:

- The Instruction Register, often abbreviated as IR, is responsible for processing an instruction from memory and helps decode the instruction

- The Program Counter, often abbreviated as PC, is responsible for pointing to the next instruction to be fetched from memory

- The Stack Pointer points to the next free position on the stack

- The Status Register contains the status of a recent operation, such as whether the result is zero, negative, or if there was an overflow condition

- The instruction cycle consists of three steps:

- Fetch: The next instruction is fetched from the memory address stored in the PC and placed in the IR. The PC is then incremented.

- Decode: The instruction is decoded. If additional memory accesses are required to read operands, it happens here.

- Execute: The instruction is executed by the control unit making use of the ALU as required. The PC can also be updated if so indicated.

Exercises[edit]

- M1022-10 Complete Merlin Mission Manager Mission M1022-10.